# 3A, Radiation Hardened, Positive, Ultra Low Dropout Regulator

# **ISL75051SRH**

The ISL75051SRH is a radiation hardened low-voltage, high-current, single-output LDO specified for up to 3.0A of continuous output current. These devices operate over an input voltage range of 2.2V to 6.0V and are capable of providing output voltages of 0.8V to 5.0V adjustable based on resistor divider setting. Dropout voltages as low as 65mV can be realized using the device.

The OCP pin allows the short-circuit output current limit threshold to be programmed by means of a resistor from the OCP pin to GND. The OCP setting range is from 0.5A minimum to 8.5A maximum. The resistor sets the constant current threshold for the output under fault conditions. The thermal shutdown disables the output if the device temperature exceeds the specified value. It subsequently enters an ON/OFF cycle until the fault is removed. The ENABLE feature allows the part to be placed into a low current shutdown mode that typically draws about 1µA. When enabled, the device operates with a typical low ground current of 11mA, which provides for operation with low quiescent power consumption.

The device is optimized for fast transient response and single event effects. This reduces the magnitude of SET seen on the output. Additional protection diodes and filters are not needed. The device is stable with tantalum capacitors as low as  $47\mu F$  and provides excellent regulation all the way from no load to full load. Programmable soft-start allows the user to program the inrush current by means of the decoupling capacitor value used on the BYP pin.

# **Applications**

- · LDO regulator for space application

- DSP, FPGA and µP core power supplies

- · Post-regulation of switched mode power supplies

- · Down-hole drilling

### **Features**

- DLA SMD#5962-11212

- Output current up to 3.0A at T<sub>I</sub> = +150°C

- Output accuracy ±1.5% over MIL temperature range

- · Ultra low dropout:

- 65mV typ dropout at 1.0A

- 225mV typ dropout at 3.0A

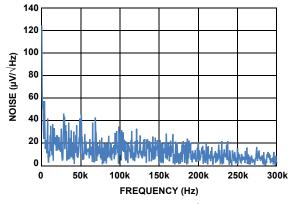

- Noise of 100µV<sub>RMS</sub> from 300Hz to 300kHz

- · SET mitigation with no added filtering/diodes

- Input supply range: 2.2V to 6.0V

- · Fast load transient response

- Shutdown current of 1µA typ

- · Output adjustable using external resistors

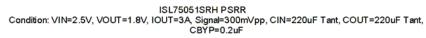

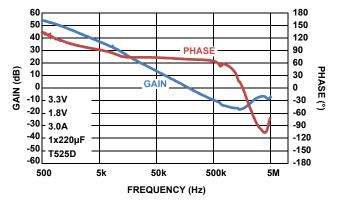

- PSRR 66dB typ at 1kHz

- Enable and PGood feature

- · Programmable soft-start/inrush current limiting

- Adjustable overcurrent limit from 0.5A to 8.5A

- · Over-temperature shutdown

- Stable with 47µF min tantalum capacitor

- 18 Ld ceramic flatpack package

- · Radiation environment

### **Related Literature**

- AN1666, "Single Event Effects Testing of the ISL75051SRH LDO"

- AN1667, "ISL75051SRH High Performance 3A LDO Evaluation Board User Guide"

- AN1947, "Intersil's Radiation Hardened Low Power FPGA Power Solutions"

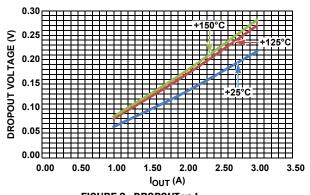

FIGURE 2. DROPOUT vs I<sub>OUT</sub>

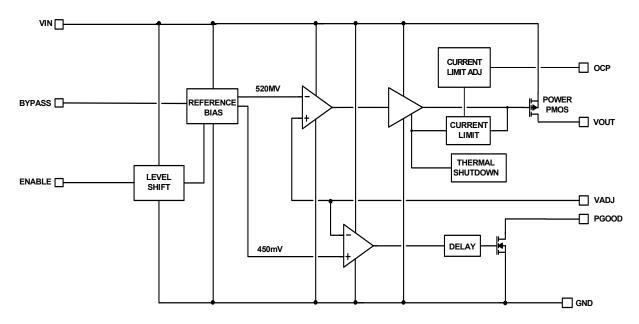

# **Block Diagram**

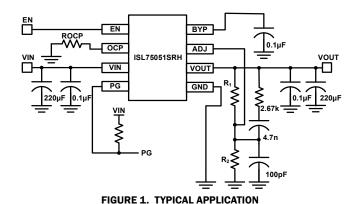

# **Typical Applications**

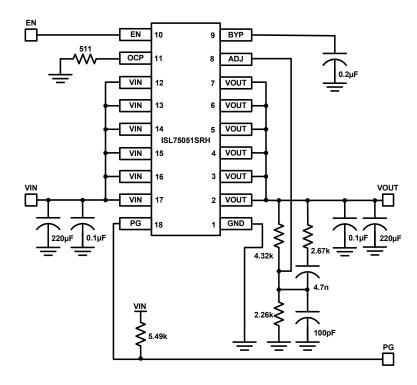

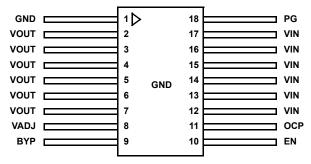

# **Pin Configuration**

ISL75051SRH (18 LD CDFP) TOP VIEW

NOTE: The ESD triangular mark is indicative of pin #1. It is a part of the device marking and is placed on the lid in the quadrant where pin #1 is located.

# **Pin Descriptions**

| PIN NUMBER               | PIN NAME | DESCRIPTION                                                                                                                        |

|--------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------|

| 12, 13, 14<br>15, 16, 17 | VIN      | Input supply pins                                                                                                                  |

| 18                       | PG       | V <sub>OUT</sub> in regulation signal. Logic low defines when V <sub>OUT</sub> is not in regulation. Must be grounded if not used. |

| 1                        | GND      | GND pin                                                                                                                            |

| 2, 3, 4<br>5, 6, 7       | VOUT     | Output voltage pins                                                                                                                |

| 8                        | VADJ     | VADJ pin allows V <sub>OUT</sub> to be programmed with an external resistor divider.                                               |

| 9                        | ВҮР      | To filter the internal reference, connect a 0.1µF capacitor from BYP pin to GND.                                                   |

| 10                       | EN       | V <sub>IN</sub> independent chip enable. TTL and CMOS compatible.                                                                  |

| 11                       | ОСР      | Allows current limit to be programmed with an external resistor.                                                                   |

| Top Lid                  | GND      | The top lid is connected to GND pin of the package.                                                                                |

# **Ordering Information**

| ORDERING NUMBER (Notes 1, 2) | PART NUMBER         | TEMP RANGE (°C) | PACKAGE<br>(ROHS COMPLIANT) | PKG DWG. # |

|------------------------------|---------------------|-----------------|-----------------------------|------------|

| 5962R1121201VXC              | ISL75051SRHVF       | -55 to +125     | 18 Ld CDFP                  | K18.D      |

| 5962R1121201QXC              | ISL75051SRHQF       | -55 to +125     | 18 Ld CDFP                  | K18.D      |

| 5962R1121201V9A              | ISL75051SRHVX       | -55 to +125     | Die                         |            |

| ISL75051SRHX/SAMPLE          | ISL75051SRHX/SAMPLE | -55 to +125     | Die Sample                  |            |

| ISL75051SRHF/PROTO           | ISL75051SRHF/PROTO  | -55 to +125     | 18 Ld CDFP                  | K18.D      |

| ISL75051SRHEVAL1Z            | Evaluation Board    |                 |                             |            |

#### NOTES:

- 1. These Intersil Pb-free Hermetic packaged products employ 100% Au plate e4 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations.

- 2. Specifications for Rad Hard QML devices are controlled by the Defense Logistics Agency Land and Maritime (DLA). The SMD numbers listed in this "Ordering Information" table must be used when ordering.

Submit Document Feedback 3 intersil FN7610.3

December 15, 2014

### **Absolute Maximum Ratings**

| V <sub>IN</sub> Relative to GND (Note 3)0.3 to     | +6.7V |

|----------------------------------------------------|-------|

| V <sub>OUT</sub> Relative to GND (Note 3)          | +6.7V |

| PG, EN, OCP/ADJ Relative to GND (Note 3)0.3 to +6. | .7VDC |

| Junction Temperature (T <sub>J</sub> ) +1          | l75°C |

| ESD Rating                                         |       |

| Human Body Model (Tested per MIL-PRF-883 3015.7)   | . 2kV |

| Machine Model (Tested per JESD22-A115-A)           | 200V  |

| Charged Device Model (Tested per JESD22-C101D)     | 750V  |

# Recommended Operating Conditions (Note 4)

| Ambient Temperature Range (T <sub>A</sub> )     | 55°C to +125°C |

|-------------------------------------------------|----------------|

| Junction Temperature (T <sub>J</sub> ) (Note 3) | +150°C         |

| V <sub>IN</sub> Relative to GND                 |                |

| V <sub>OUT</sub> Range                          | 0.8V to 5.0V   |

| PG, EN, OCP/ADJ relative to GND                 | 0V to +6.0V    |

#### **Thermal Information**

| Thermal Resistance (Typical)    | $\theta_{JA}$ (°C/W) | $\theta_{JC}$ (°C/W) |

|---------------------------------|----------------------|----------------------|

| 18 Ld CDFP Package (Notes 5, 6) | 28                   | 4                    |

| Storage Temperature Range       | 6!                   | 5°C to +150°C        |

| Pb-Free Reflow Profile          |                      | see <u>TB493</u>     |

#### **Radiation Information**

| Max Total Dose                                                                   |                                            |

|----------------------------------------------------------------------------------|--------------------------------------------|

| (Dose Rate = 50 - 300radSi/s                                                     | 100krad (Si)                               |

| SET (V <sub>OUT</sub> < ±5% During Events) (Note 7)                              | . 86MeV·cm <sup>2</sup> /mg                |

| SEL/B (No Latch-up/Burnout)                                                      | . 86MeV·cm <sup>2</sup> /mg                |

| The output capacitance used for SEE testing is $220\mu\text{F}$ 200nF for BYPASS | for C <sub>IN</sub> and C <sub>OUT</sub> , |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- 3. Extended operation at these conditions may compromise reliability. Exceeding these limits will result in damage. Recommended operating conditions define limits where specifications are guaranteed.

- 4. Refer to "Thermal Guidelines" on page 12.

- 5. θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief <u>TB379</u>

- 6. For  $\theta_{\mbox{\scriptsize JC}},$  the "case temp" location is the center of the package underside.

- 7. The device can work down to  $V_{OUT} = 0.8V$ ; however, the SET performance of  $< \pm 5\%$  at LET = 86MeV cm2/mg is guaranteed at  $V_{OUT} = > 1.5V$  only. SET tests performed with  $220\mu F$  10V  $25m\Omega$  and  $0.1\mu F$  CDR04 capacitor on the input and output.

**Electrical Specifications** Unless otherwise noted, all parameters are guaranteed over the following specified conditions:  $V_{IN} = V_{OUT} + 0.4V$ ,  $V_{OUT} = 1.8V$ ,  $C_{IN} = C_{OUT} = 220 \mu F$  25mΩ and  $0.1 \mu F$  X7R,  $T_J = +25 \,^{\circ}$ C,  $I_L = 0A$ . Applications must follow thermal guidelines of the package to determine worst-case junction temperature (Note 8). Boldface limits apply across the operating temperature range, -55  $\,^{\circ}$ C to +125  $\,^{\circ}$ C. Pulse load techniques used by ATE to ensure  $T_J = T_A$  defines guaranteed limits.

| PARAMETER                  | SYMBOL           | TEST CONDITIONS                                                                                                | MIN<br>( <u>Note 9</u> ) | TYP   | MAX<br>( <u>Note 9</u> ) | UNITS |

|----------------------------|------------------|----------------------------------------------------------------------------------------------------------------|--------------------------|-------|--------------------------|-------|

| DC CHARACTERISTICS         |                  |                                                                                                                |                          | l.    |                          |       |

| DC Output Voltage Accuracy | V <sub>OUT</sub> | V <sub>OUT</sub> V <sub>OUT</sub> Resistor adjust to 0.52V, 1.5V and 1.8V                                      |                          |       |                          |       |

|                            |                  | 2.2V < V <sub>IN</sub> < 3.6V; 0A < I <sub>LOAD</sub> < 3.0A                                                   | -1.5                     | 0.2   | 1.5                      | %     |

|                            |                  | V <sub>OUT</sub> Resistor adjust to 5.0V                                                                       |                          |       | •                        |       |

|                            |                  | V <sub>OUT</sub> + 0.4V < V <sub>IN</sub> < 6.0V; 0A < I <sub>LOAD</sub> < 3.0A                                | -1.5                     | 0.2   | 1.5                      | %     |

| Feedback Pin               | V <sub>ADJ</sub> | 2.2V < V <sub>IN</sub> < 6.0V; I <sub>LOAD</sub> = 0A                                                          | 514.8                    | 520   | 525.2                    | mV    |

| BYP Pin                    | V <sub>BYP</sub> | 2.2V < V <sub>IN</sub> < 6.0V; I <sub>LOAD</sub> = 0A                                                          |                          | 520   |                          | mV    |

| DC Input Line Regulation   |                  | 2.2V < V <sub>IN</sub> < 3.6V, V <sub>OUT</sub> = 1.5V, +25°C and -55°C (Note 10)                              |                          | 1.13  | 3.5                      | mV    |

|                            |                  | 2.2V < V <sub>IN</sub> < 3.6V, V <sub>OUT</sub> = 1.5V, +125°C ( <u>Note 10</u> )                              |                          | 1.13  | 8.0                      | mV    |

|                            |                  | 2.2V < V <sub>IN</sub> < 3.6V, V <sub>OUT</sub> = 1.8V, +25°C and -55°C (Note 10)                              |                          | 1.62  | 3.5                      | mV    |

|                            |                  | 2.2V < V <sub>IN</sub> < 3.6V, V <sub>OUT</sub> = 1.8V, +125°C ( <u>Note 10</u> )                              |                          | 1.62  | 10.5                     | mV    |

|                            |                  | V <sub>OUT</sub> + 0.4V < V <sub>IN</sub> < 6.0V, V <sub>OUT</sub> = 5.0V ( <u>Note 10</u> )                   |                          | 12.50 | 20.0                     | mV    |

| DC Output Load Regulation  |                  | V <sub>OUT</sub> = 1.5V; 0A < I <sub>LOAD</sub> < 3.0A, V <sub>IN</sub> = V <sub>OUT</sub> + 0.4V<br>(Note 10) | -4.0                     | -0.8  | -0.1                     | mV    |

|                            |                  | V <sub>OUT</sub> = 1.8V; 0A < I <sub>LOAD</sub> < 3.0A, V <sub>IN</sub> = V <sub>OUT</sub> + 0.4V<br>(Note 10) | -4.0                     | -1.2  | -0.05                    | mV    |

|                            |                  | V <sub>OUT</sub> = 5.0V; 0A < I <sub>LOAD</sub> < 3.0A, V <sub>IN</sub> = V <sub>OUT</sub> + 0.4V<br>(Note 10) | -15.0                    | -6.0  | -0.05                    | mV    |

| Feedback Input Current     |                  | V <sub>ADJ</sub> = 0.5V                                                                                        |                          |       | 1                        | μΑ    |

Submit Document Feedback 4 intersil FN7610.3

December 15, 2014

**Electrical Specifications** Unless otherwise noted, all parameters are guaranteed over the following specified conditions: V<sub>IN</sub> = V<sub>OUT</sub> + 0.4V,  $V_{OUT}$  = 1.8V,  $C_{IN}$  =  $C_{OUT}$  = 220 $\mu$ F 25m $\Omega$  and  $0.1\mu$ F X7R,  $T_J$  = +25°C,  $I_L$  = 0A. Applications must follow thermal guidelines of the package to determine worst-case junction temperature (Note 8). Boldface limits apply across the operating temperature range, -55°C to +125°C. Pulse load techniques used by ATE to ensure  $T_J = T_A$  defines guaranteed limits. (Continued)

| PARAMETER                                      | SYMBOL            | TEST CONDITIONS                                                                          | MIN<br>( <u>Note 9</u> ) | TYP  | MAX<br>( <u>Note 9</u> ) | UNITS             |

|------------------------------------------------|-------------------|------------------------------------------------------------------------------------------|--------------------------|------|--------------------------|-------------------|

| Ground Pin Current                             | lQ                | V <sub>OUT</sub> = 1.5V; I <sub>LOAD</sub> = 0A, V <sub>IN</sub> = 2.2V                  |                          | 11   | 12                       | mA                |

|                                                |                   | $V_{OUT} = 5.0V; I_{LOAD} = 0A, V_{IN} = 6.0V$                                           |                          | 16   | 18                       | mA                |

|                                                |                   | $V_{OUT} = 1.5V$ ; $I_{LOAD} = 3.0A$ , $V_{IN} = 2.2V$                                   |                          | 11   | 13                       | mA                |

|                                                |                   | V <sub>OUT</sub> = 5.0V; I <sub>LOAD</sub> = 3.0A, V <sub>IN</sub> = 6.0V                |                          | 16   | 18                       | mA                |

| Ground Pin Current in Shutdown                 | I <sub>SHDN</sub> | ENABLE Pin = OV, V <sub>IN</sub> = 6.0V                                                  |                          | 1    | 10                       | μΑ                |

| Dropout Voltage                                | V <sub>DO</sub>   | I <sub>LOAD</sub> = 1.0A, V <sub>OUT</sub> = 2.5V ( <u>Note 11</u> )                     |                          | 65   | 100                      | m۷                |

|                                                |                   | I <sub>LOAD</sub> = 2.0A, V <sub>OUT</sub> = 2.5V ( <u>Note 11</u> )                     |                          | 140  | 200                      | mV                |

|                                                |                   | I <sub>LOAD</sub> = 3.0A, V <sub>OUT</sub> = 2.5V ( <u>Note 11</u> )                     |                          | 225  | 300                      | mV                |

| Output Short-circuit Current                   | ISCL              | V <sub>OUT</sub> = 0V, V <sub>IN</sub> = 2.2V, R <sub>SET</sub> = 5.11k                  |                          | 1.1  |                          | Α                 |

|                                                |                   | V <sub>OUT</sub> = 0V, V <sub>IN</sub> = 6.0V, R <sub>SET</sub> = 5.11k                  |                          | 1.2  |                          | Α                 |

|                                                | ISCH              | $V_{OUT} = 0V, V_{IN} = 2.2V, R_{SET} = 511\Omega$                                       |                          | 5.7  |                          | Α                 |

|                                                |                   | $V_{OUT} = 0V, V_{IN} = 6.0V, R_{SET} = 511\Omega$                                       |                          | 6.2  |                          | Α                 |

| Thermal Shutdown Temperature                   | TSD               | V <sub>OUT</sub> + 0.4V < V <sub>IN</sub> < 6.0V                                         |                          | 175  |                          | °C                |

| Thermal Shutdown Hysteresis (Rising Threshold) | TSDn              | V <sub>OUT</sub> + 0.4V < V <sub>IN</sub> < 6.0V                                         |                          | 25   |                          | °C                |

| AC CHARACTERISTICS                             |                   |                                                                                          |                          |      |                          | 1                 |

| Input Supply Ripple Rejection                  | PSRR              | $V_{P-P} = 300$ mV, f = 1kHz, $I_{LOAD} = 3$ A; $V_{IN} = 2.5$ V, $V_{OUT} = 1.8$ V      | 42                       | 66   |                          | dB                |

|                                                |                   | $V_{P-P} = 300$ mV, $f = 100$ kHz, $I_{LOAD} = 3$ A; $V_{IN} = 2.5$ V, $V_{OUT} = 1.8$ V |                          | 30   |                          | dB                |

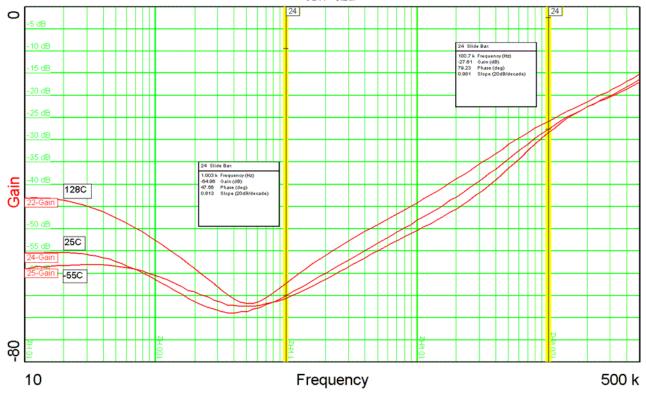

| Phase Margin                                   | PM                | V <sub>OUT</sub> = 1.8V, C <sub>L</sub> = 220μF Tantalum                                 |                          | 70   |                          | dB                |

| Gain Margin                                    | GM                | V <sub>OUT</sub> = 1.8V, C <sub>L</sub> = 220μF Tantalum                                 |                          | 16   |                          | dB                |

| Output Noise Voltage                           |                   | I <sub>LOAD</sub> = 10mA, BW = 300Hz < f < 300kHz, BYPASS<br>to GND capacitor = 0.2µF    |                          | 100  |                          | μV <sub>RMS</sub> |

| DEVICE START-UP CHARACTERIST                   | ICS: ENABLE       | PIN                                                                                      |                          | 1    | 1                        | 1                 |

| Rising Threshold                               |                   | 2.2V < V <sub>IN</sub> < 6.0V                                                            | 0.6                      | 0.9  | 1.2                      | V                 |

| Falling Threshold                              |                   | 2.2V < V <sub>IN</sub> < 6.0V                                                            | 0.47                     | 0.7  | 0.9                      | V                 |

| Enable Pin Leakage Current                     |                   | V <sub>IN</sub> = 6.0V, EN = 6.0V                                                        |                          |      | 1                        | μΑ                |

| Enable Pin Propagation Delay                   |                   | V <sub>IN</sub> = 2.2V, EN rise to I <sub>OUT</sub> rise                                 | 225                      | 300  | 450                      | μs                |

| Hysteresis                                     |                   | Must be independent of V <sub>IN</sub> ; 2.2V < V <sub>IN</sub> < 6.0V                   | 90                       | 200  | 318                      | mV                |

| DEVICE START-UP CHARACTERIST                   | ICS: PG PIN       |                                                                                          |                          |      |                          | 1                 |

| V <sub>OUT</sub> Error Flag Rising Threshold   |                   | 2.2V < VIN < 6.0V                                                                        | 85                       | 90   | 96                       | %                 |

| V <sub>OUT</sub> Error Flag Falling Threshold  |                   | 2.2V < VIN < 6.0V                                                                        | 82                       | 88   | 93                       | %                 |

| V <sub>OUT</sub> Error Flag Hysteresis         |                   | 2.2V < VIN < 6.0V                                                                        | 2.5                      | 3.2  | 4.0                      | %V <sub>OUT</sub> |

| Error Flag Low Voltage                         |                   | I <sub>SINK</sub> = 1mA                                                                  |                          | 35   | 100                      | mV                |

|                                                |                   | I <sub>SINK</sub> = 6mA                                                                  |                          | 185  | 400                      | mV                |

| Error Flag Leakage Current                     |                   | V <sub>IN</sub> = 6.0V, PG = 6.0V                                                        |                          | 0.01 | 1                        | μΑ                |

#### NOTES:

- 8. Refer to "Applications Information" on page 10 of the datasheet and Tech Brief TB379.

- 9. Parameters with MIN and/or MAX limits are 100% tested at -55°C, +25°C and +125°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

- 10. Line and Load Regulation done under pulsed condition for T<10ms.

- 11. Dropout is defined as the difference between the supply  $V_{IN}$  and  $V_{OUT}$ , when the supply produces a 2% drop in  $V_{OUT}$  from its nominal value. Data measured within a 3ms period.

Submit Document Feedback intersil FN7610.3 December 15, 2014

# **Typical Operating Performance**

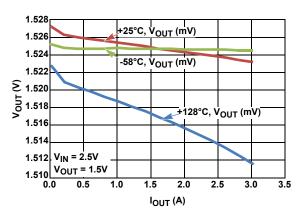

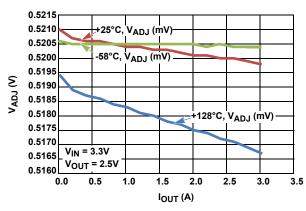

FIGURE 3. LOAD REGULATION,  $V_{OUT}$  vs  $I_{OUT}$

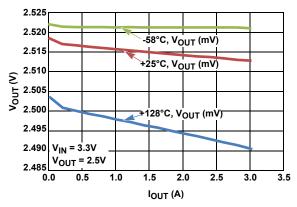

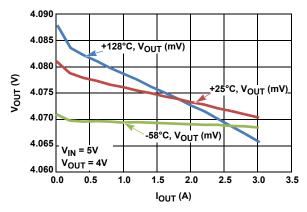

FIGURE 5. LOAD REGULATION,  $V_{OUT}$  vs  $I_{OUT}$

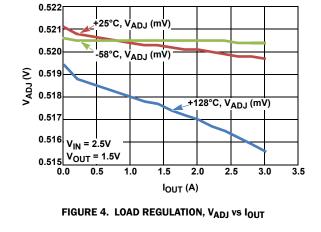

FIGURE 6. LOAD REGULATION,  $V_{ADJ}$  vs  $I_{OUT}$

FIGURE 7. LOAD REGULATION,  $V_{OUT}$  vs  $I_{OUT}$

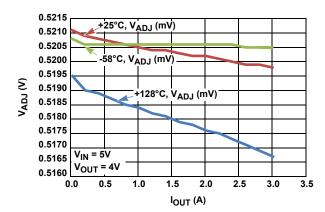

FIGURE 8. LOAD REGULATION, V<sub>ADJ</sub> vs I<sub>OUT</sub>

# Typical Operating Performance (Continued)

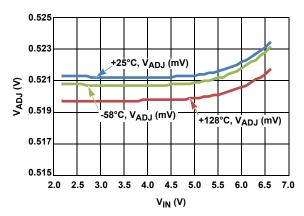

FIGURE 9.  $V_{IN}$  vs  $V_{ADJ}$  OVER-TEMPERATURE

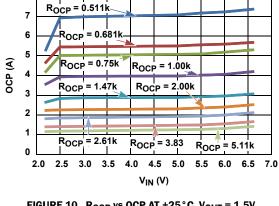

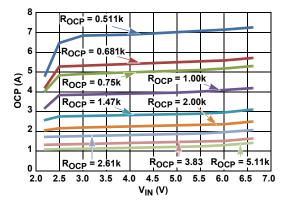

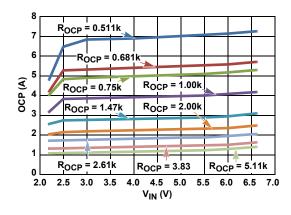

FIGURE 10. R<sub>OCP</sub> vs OCP AT +25°C, V<sub>OUT</sub> = 1.5V

FIGURE 11. R<sub>OCP</sub> vs OCP AT +128°C, V<sub>OUT</sub> = 1.5V

FIGURE 12. R<sub>OCP</sub> vs OCP AT -58°C, V<sub>OUT</sub> = 1.5V

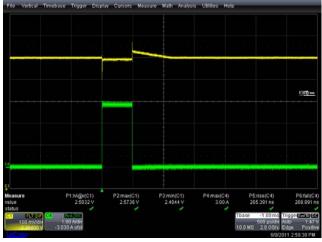

FIGURE 13. TRANSIENT LOAD RESPONSE,  $V_{IN} = 3.3V$ ,  $V_{OUT} = 2.5V$ ,  $\textbf{C}_{\textbf{OUT}} = 47 \mu \textbf{F},\, 35 \text{m} \Omega$

FIGURE 14. TRANSIENT LOAD RESPONSE,  $V_{IN} = 3.3V$ ,  $V_{OUT} = 2.5V$ ,  $C_{OUT}$  = 220 $\mu$ F, 25m $\Omega$

# Typical Operating Performance (Continued)

FIGURE 15. POWER-ON AND POWER-OFF, EN = 0 TO 1, +25°C, V<sub>IN</sub> = 6V, V<sub>OUT</sub> = 0.8V, I<sub>OUT</sub> = 0.5A, PGOOD TURN-ON

FIGURE 17. POWER-ON AND POWER-OFF, EN = 1 TO 0, +25 °C,  $V_{IN}$  = 6V,  $V_{OUT}$  = 0.8V,  $I_{OUT}$  = 0.5A, PGOOD **TURN-OFF**

FIGURE 16. POWER-ON AND POWER-OFF, EN = 0 TO 1, +25°C, V<sub>IN</sub> = 2.2V, V<sub>OUT</sub> = 0.8V, I<sub>OUT</sub> = 0.5A, PGOOD TURN-ON

FIGURE 18. POWER-ON AND POWER-OFF, EN = 1 TO 0,  $+25\,^{\circ}$ C,  $V_{IN}$  = 2.2V,  $V_{OUT}$  = 0.8V,  $I_{OUT}$  = 0.5A, PG00D **TURN-OFF**

FIGURE 19. NOISE ( $\mu V/\sqrt{Hz}$ )

Submit Document Feedback intersil FN7610.3 December 15, 2014

# Typical Operating Performance (Continued)

FIGURE 20. PSRR

# **Applications Information**

### **Input Voltage Requirements**

This RH LDO will work from a  $\mathrm{V}_{IN}$  in the range of 2.2V to 6.0V. The input supply can have a tolerance of as much as ±10% for conditions noted in the "Electrical Specifications" table starting on page 4. Minimum guaranteed input voltage is 2.2V. However, due to the nature of an LDO, V<sub>IN</sub> must be some margin higher than the output voltage, plus dropout at the maximum rated current of the application, if active filtering (PSRR) is expected from  $V_{IN}$  to  $V_{OUT}$ . The dropout spec of this family of LDOs has been generously specified to allow applications to design for efficient operation.

### **Adjustable Output Voltage**

The output voltage of the RH LDO can be set to any user programmable level between 0.8V to 5.0V. This is achieved with a resistor divider connected between the OUT, ADJ and GND pins. With the internal reference at 0.52V, the divider ratio should be fixed such that when the desired VOUT level is reached, the voltage presented to the ADJ pin is 0.52V. Resistor values for typical voltages are shown in Table 1.

**TABLE 1. RESISTOR VALUES FOR TYPICAL VOLTAGES**

| V <sub>OUT (V)</sub> | R <sub>BOTTOM</sub> | R <sub>TOP</sub> (k) |

|----------------------|---------------------|----------------------|

| 0.8                  | 7.87k               | 4.32                 |

| 1.5                  | 2.26k               | 4.32                 |

| 1.8                  | 1.74k               | 4.32                 |

| 2.5                  | 1.13k               | 4.32                 |

| 4.0                  | 634                 | 4.32                 |

| 5.0                  | 499                 | 4.32                 |

$$\mathsf{BOTTOM} = \frac{\mathsf{R}_{\mathsf{TOP}}}{\left(\frac{\mathsf{V}_{\mathsf{OUT}}}{\mathsf{V}_{\mathsf{IDI}}}\right) - \mathbf{1}} \tag{EQ. 1}$$

### **Input and Output Capacitor Selection**

RH operation requires the use of a combination of tantalum and ceramic capacitors to achieve a good volume-to-capacitance ratio. The recommended combination is a 220 $\mu$ F, 25m $\Omega$  10V DSSC 04051-032 rated tantalum capacitor in parallel with a 0.1µF MIL-PRF-49470 CDR04 ceramic capacitor, to be connected between VIN to GND pins and VOUT to GND pins of the LDO, with PCB traces no longer than 0.5cm.

The stability of the device depends on the capacitance and ESR of the output capacitor. The usable ESR range for the device is  $6m\Omega$  to  $100m\Omega$ . At the lower limit of ESR =  $6m\Omega$ , the phase margin is about +51°C. On the high side, an ESR of  $100m\Omega$  is found to limit the gain margin at around 10dB. The typical GM/PM seen with capacitors are shown in Table 2.

TABLE 2. TYPICAL GM/PM WITH VARIOUS CAPACITORS

| CAPACITANCE (µF) | ESR<br>(mΩ) | GAIN MARGIN<br>(dB) | PHASE MARGIN (°) |

|------------------|-------------|---------------------|------------------|

| 47               | 35          | 14                  | 55               |

| 100              | 25          | 16                  | 57               |

| 220              | 6           | 19                  | 51               |

| 220              | 25          | 16                  | 69               |

| 100              | 100         | 10                  | 62               |

Type numbers of KEMET capacitors used in the device are shown in Table 3.

TABLE 3. KEMET CAPACITORS USED IN DEVICE

| KEMET TYPE NUMBER  | CAPACITOR DETAILS |

|--------------------|-------------------|

| T525D476M016ATE035 | 47μF, 10V, 35mΩ   |

| T525D107M010ATE025 | 100μF, 10V, 25mΩ  |

| T530D227M010ATE006 | 220μF, 10V, 6mΩ   |

| T525D227M010ATE025 | 220μF, 10V, 25mΩ  |

| T495X107K016ATE100 | 100μF, 16V, 100mΩ |

A typical gain phase plot measured on the ISL75051SRHEVAL1Z evaluation board for  $V_{IN} = 3.3V$ ,  $V_{OUT} = 1.8V$  and  $I_{OUT} = 3A$  with a 220 $\mu$ F, 10V, 25m $\Omega$  capacitor is shown in Figure 21 and is measured at GM = 16.3dB and PM = 69.16°.

FIGURE 21. TYPICAL GAIN PHASE PLOT

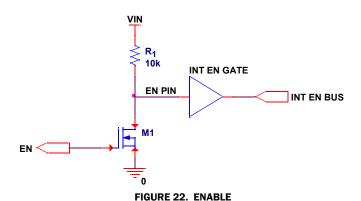

#### **Enable**

The device can be enabled by applying a logic high on the EN pin. The enable threshold is typically 0.9V. A soft-start cycle is initiated when the device is enabled using this pin. Taking this pin to logic low disables the device.

EN can be driven from either an open drain or a totem pole logic drive between EN pin and GND. Assuming an open drain configuration, M1 will actively pull down the EN line, as shown in Figure 22, and thereby discharge the input capacitance, shutting off the device immediately.

Submit Document Feedback FN7610.3 10 intersil December 15, 2014

### **Power-Good**

The Power-good pin is asserted high when the voltage on the ADJ pin crosses the rising threshold of 0.9 x V<sub>ADI</sub> typ. On the falling threshold, Power-good is asserted low when the voltage on the ADJ pin crosses the falling threshold of 0.88 x  $V_{ADJ}$ . The power-good output is an open-drain output rated for a continuous sink current of 1mA.

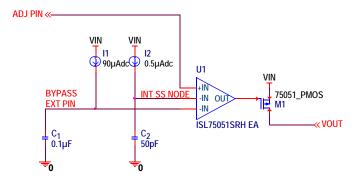

#### Soft-start

Soft-start is achieved by means of the charging time constant of the BYP pin. The capacitor value on the pin determines the time constant and can be calculated using Equations 2 through 4:

If  $V_{IN}$  range is  $2.2V \le V_{IN} < 2.7V$ :

$$\mathbf{t_{SS}} = (-4.8376 \bullet \mathbf{V_{IN}}) + (0.0254 \bullet \mathbf{T_{A}}) + (0.0522 \bullet \mathbf{C_{BYP}}) + \mathbf{11.8526}$$

(Eq. 2

If  $V_{IN}$  range is  $2.7V \le V_{IN} < 4.0V$ :

$$t_{\text{SS}} = (-\text{1.4711} \bullet \text{V}_{\text{IN}}) + (0.0179 \bullet \text{T}_{\text{A}}) + (0.0377 \bullet \text{C}_{\text{BYP}}) + 4.7430 \tag{EQ. 3}$$

If  $V_{IN}$  range is  $4.0V \le V_{IN} < 6.0V$ :

$$t_{SS} = (-0.4458 \bullet V_{IN}) + (0.0130 \bullet T_{A}) + (0.0295 \bullet C_{BYP}) + 1.8527 \tag{EQ. 4}$$

where  $t_{SS}$  = soft-start time (ms),  $V_{IN}$  = Input supply (V),  $T_A$  = Ambient Temperature and  $C_{BYP}$  = BYPASS capacitor (nF).

The BYPASS capacitor, C<sub>1</sub>, charges with a current source and provides an EA reference, -IN, with an SS ramp. VOUT, in turn, follows this ramp. The ramp rate can be calculated based on the  $C_1$  value. For conditions in which  $C_1$  is opened, or for small values of  $C_1$ , the ramp is provided by  $C_2 = 50pF$ , with a source of  $0.5\mu A$ . Connecting  $C_1$  min =  $0.1\mu F$  to the BYPASS pin is recommended for normal operation.

FIGURE 23. SOFT-START

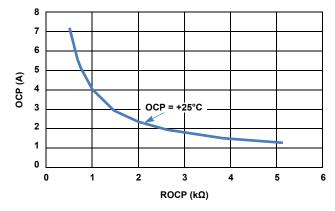

### **Current Limit Protection**

The RH LDO incorporates protection against overcurrent due to any short or overload condition applied to the output pin. The current limit circuit becomes a constant current source when the output current exceeds the current limit threshold, which can be adjusted by means of a resistor connected between the OCP pin and GND. If the short or overload condition is removed from  $V_{OUT}$ , then the output returns to normal voltage mode regulation. OCP can be calculated with Equation 5:

$$OCP = (4.1115 \times ROCP^{-0.75})$$

(EQ. 5)

where OCP = Overcurrent Threshold in amps, and ROCP = OCP resistor in kΩ.

In the event of an overload condition based on the set OCP limit, the die temperature may exceed the internal over-temperature limit, and the LDO begins to cycle on and off due to the fault condition (Figure 24). However, thermal cycling may never occur if the heatsink used for the package can keep the die temperature below the limits specified for thermal shutdown.

FIGURE 24. OCP vs ROCP OVER-TEMPERATURE

### **Thermal Guidelines**

If the die temperature exceeds typically +175°C, then the LDO output shuts down to zero until the die temperature cools to typically +155°C. The level of power combined with the thermal impedance of the package ( $\theta_{JC}$  of 4°C/W for the 18 Ld CDFP package) determines whether the junction temperature exceeds the thermal shutdown temperature specified in the "Electrical Specifications" on page 4 table.

The device should be mounted on a high effective thermal conductivity PCB with thermal vias, per JESD51-7 and JESD51-5. Place a silpad between package base and PCB copper plane. The VIN and VOUT ratios should be selected to ensure that dissipation for the selected VIN range keeps T<sub>J</sub> within the recommended operating level of +150 °C for normal operation.

Submit Document Feedback 12 FN7610.3 December 15, 2014

# **Weight Characteristics**

# **Weight of Packaged Device**

K18.D: 1.07 Grams typical with leads clipped

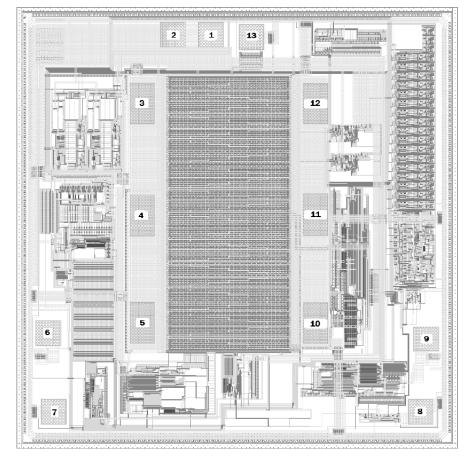

# **Die Characteristics**

#### **Die Dimensions**

$4555\mu m \ x \ 4555\mu m \ (179.3 \ mils \ x \ 179.3 \ mils)$ Thickness:  $304.8\mu m \pm 25.4\mu m \ (12.0 \ mils \pm 1 \ mil)$

### **Interface Materials**

### **GLASSIVATION**

Type: Silicon Oxide and Silicon Nitride Thickness:  $0.3\mu m \pm 0.03\mu m$  to  $1.2\mu m \pm 0.12\mu m$

#### **TOP METALLIZATION**

Type: AlCu (99.5%/0.5%) Thickness:  $2.7\mu m \pm 0.4\mu m$

#### **BACKSIDE METALLIZATION**

None

#### **SUBSTRATE**

Type: Silicon

#### **BACKSIDE FINISH**

Silicon

#### **PROCESS**

0.6µM BiCMOS Junction Isolated

#### **ASSEMBLY RELATED INFORMATION**

#### **Substrate Potential**

Unbiased

### **ADDITIONAL INFORMATION**

### **Worst Case Current Density**

$< 2 \times 10^5 \, \text{A/cm}^2$

#### **Transistor Count**

2932

# **Layout Characteristics**

# **Step and Repeat**

4555µm x 4555µm

# **Metallization Mask Layout**

| PAD X Y COORDINATES |      |           |           |  |  |

|---------------------|------|-----------|-----------|--|--|

| PAD                 | NAME | χ<br>(μm) | Υ<br>(μm) |  |  |

| 1                   | GND  | 0         | 0         |  |  |

| 2                   | GND  | -393      | 0         |  |  |

| 3                   | VOUT | -711      | -710      |  |  |

| 4                   | VOUT | -711      | -1858     |  |  |

| 5                   | VOUT | -711      | -2964     |  |  |

| 6                   | ADJ  | -1680     | -3070     |  |  |

| 7                   | BYP  | -1621     | -3879     |  |  |

| 8                   | EN   | 2164      | -3879     |  |  |

| 9                   | OCP  | 2222      | -3131     |  |  |

| 10                  | VIN  | 1078      | -2965     |  |  |

| 11                  | VIN  | 1078      | -1853     |  |  |

| 12                  | VIN  | 1078      | -711      |  |  |

| 13                  | PG   | 420       | -25       |  |  |

# **Revision History**

The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please go to web to make sure you have the latest revision.

| DATE               | REVISION | CHANGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| December 15, 2014  | FN7610.3 | Made correction to Charged Device Model testing information from Tested per CDM-22Cl0ID to JESD22-C101D. Replaced Equation 2 and added Equations 3 and 4 on page 11.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| October 27, 2014   |          | Added AN1947 reference to the Related Literature section on page 1.  Added ESD ratings under the Abs Max section on page 4.  Human Body Model (Tested per MIL-PRF-883 3015.7)2.5kV  Machine Model (Tested per JESD22-A115-A)                                                                                                                                                                                                                                                                                                                                                                     |

|                    |          | Charged Device Model (Tested per CDM-22CIOID)1kV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| April 15, 2014     | FN7610.2 | 1) Equation 2 Changed From: Trise (ms)=0.00577xCss (nF) To: Trise (ms)=0.0326xCss (nF). 2) Changed From: "a 90µA source current " To: " a current source". 3) Added a note to the pin configuration figure on page 3 and note 2 to Ordering information table on page 3. 4) Equation 5 Changed From: OCP = 9.5 • EXP(-0.6 • (ROCP / (1 + 0.1ROCP))) TO: OCP = 4.1115 x ROCP <sup>-0.75</sup> 5) Updated POD for k18.D from Rev3 to Rev5. 6) Updated Table 1 headings. 7) Added Equation 1 to page 10. 8) Removed both "Enable Pin Turn-on Delay" rows from "Electrical Specifications" on page 5 |

| November 4, 2011   | FN7610.1 | Removed "Coming Soon" from ISL75051SRHVF, ISL75051SRHQF, ISL75051SRHVX and ISL75051SRHX/SAMPLE in "Ordering Information" table on page 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| September 30, 2011 | FN7610.0 | Initial Release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

# **About Intersil**

Intersil Corporation is a leading provider of innovative power management and precision analog solutions. The company's products address some of the largest markets within the industrial and infrastructure, mobile computing and high-end consumer markets.

For the most updated datasheet, application notes, related documentation and related parts, please see the respective product information page found at www.intersil.com.

You may report errors or suggestions for improving this datasheet by visiting www.intersil.com/ask.

Reliability reports are also available from our website at www.intersil.com/support

For additional products, see www.intersil.com/en/products.html

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted in the quality certifications found at www.intersil.com/en/support/qualandreliability.html

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

intersil FN7610.3 14 December 15, 2014

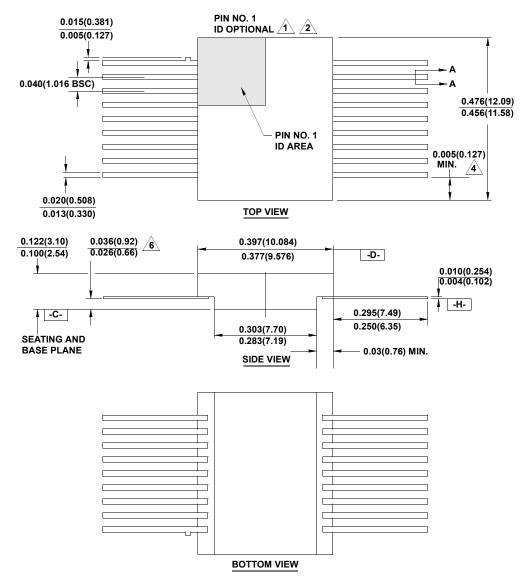

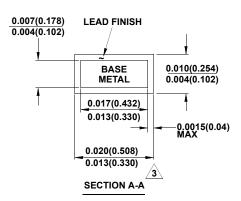

# Package Outline Drawing K18.D

18 LEAD CERAMIC METAL SEAL FLATPACK PACKAGE

Rev 5, 3/13

#### NOTES:

- 1. Index area: A notch or a pin one identification mark shall be located adjacent to pin one and shall be located within the shaded area shown. The manufacturer's identification shall not be used as a pin one identification mark. Alternately, a tab may be used to identify pin one.

- 2. If a pin one identification mark is used in addition to a tab, the limits of the tab dimension do not apply.

- 3. The maximum limits of lead dimensions (section A-A) shall be measured at the centroid of the finished lead surfaces, when solder dip or tin plate lead finish is applied.

- 4. Measure dimension at all four corners.

- 5. For bottom-brazed lead packages, no organic or polymeric materials shall be molded to the bottom of the package to cover the leads.

- 6. Dimension shall be measured at the point of exit (beyond the meniscus) of the lead from the body. Dimension minimum shall be reduced by 0.0015 inch (0.038mm) maximum when solder dip lead finish is applied.

- 7. Dimensioning and tolerancing per ANSI Y14.5M 1982.

- 8. Dimensions = INCH (mm). Controlling dimension: INCH.

Submit Document Feedback 15 intersil FN7610.3